### ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ

Нижегородский государственный университет им. Н.И. Лобачевского

Е.И. Шкелев

# Аппаратные средства вычислительной техники

Учебное пособие

Рекомендовано ученым советом радиофизического факультета для студентов ННГУ, обучающихся по направлениям подготовки 010800 «Радиофизика» и 090106 «Информационная безопасность телекоммуникационных систем»

Нижний Новгород 2010 УДК 681.3 ББК 32.973.2 Ш-66

Ш-66 Шкелев Е.И. АППАРАТНЫЕ СРЕДСТВА ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ: Учебное пособие. – Нижний Новгород: Нижегородский госуниверситет, 2010. – 222 с.

#### Рецензенты:

заведующий кафедрой теории цепей и телекоммуникаций ИРИТ Нижегородского государственного технического университета им. Р.Е. Алексеева д. ф.-м. н профессор В.И. Есипенко, профессор кафедры бионики и статистической радиофизики Нижегородского государственного университета им. Н.И. Лобачевского д.т.н. В.Т. Ермолаев

В пособии изложены логика работы и схемотехнические решения цифровых функциональных узлов, включая базовые логические элементы, комбинационные схемы для выполнения логических и вычислительных операций и цифровые автоматы. К последним относятся элементы памяти (триггеры), запоминающие устройства и различной степени сложности машины состояний от регистров и двоичных счетчиков до арифметическо-логического устройства и микропрограммного автомата как основы для построения процессорных элементов (микропроцессоров, в частности). Рассмотрены архитектурные решения логика работы центрального И процессора (микропроцессора), особенности CISC- и RISC-архитектуры, построение и функциональный состав микропроцессорных систем, включая машину фон-Неймана, системы с гарвардской архитектурой и многопроцессорные системы. Приводятся примеры построения микроконтроллеров, цифровых процессоров сигналов и процессоров общего назначения.

Учебное пособие предназначено для студентов третьего-четвертого курсов естественнонаучных и технических высших учебных заведений, изучающих цифровые вычислительные устройства и устройства цифровой обработки сигналов, включая программируемую логику, микропроцессоры и микропроцессорные системы.

УДК 681.3 ББК 32.973.2

©Нижегородский государственный университет им. Н.И. Лобачевского, 2010

### Предисловие

Предмет, которому посвящено данное учебное пособие, можно рассматривать с разных точек зрения. Выделим две из них. Первая направлена на аппаратную реализацию цифровых вычислительных систем (ВС). Вторая связана с механизмом перемещения информации внутри системы и со способами взаимодействия ВС с внешними по отношению к ней устройствами.

Если вычислительное устройство представить как систему, основным элементом которой является процессор, то при ее реализации потребуется решить

- какие компоненты включить в состав процессорной системы,

- какими средствами поддерживать их работу,

- как обеспечить взаимодействие компонент системы друг с другом и функционирование вычислительной системы вцелом,

- каковы способы передачи и способы селекции сигналов, которыми обмениваются компоненты системы,

- каковы конструктивное оформление и регламент работы используемых при этом линий (каналов) связи.

Принцип действия современных, как и ранее созданных электронных цифровых устройств во многом остается неизменным. Существенно меняется элементная база, основой которой стали микросхемы, разнообразные как по уровню интеграции, так и по функциональным возможностям и принадлежности.

В пособии рассмотрены составные части и логика работы цифровых функциональных узлов разной степени сложности, начиная от простейших логических элементов до сложных цифровых автоматов, каковым является, например, микропрограммный автомат. В отдельный раздел вынесены вопросы, связанные с иерархией памяти, поддержкой виртуального адресного пространства, функционированием кэш-памяти построением И систем. многопроцессорных Показывается, обобщенная как выглядит архитектура и алгоритм работы центрального процессора (ЦП) и какие функциональные узлы должны входить в его состав. Обсуждаются особенности CISC и RISC процессоров, вопросы конвейеризации и распараллеливания вычислительных операций. Рассматривается работа процессорной системы в целом, механизм взаимодействия процессора, памяти и устройств вводаархитектурные решения микропроцессорных систем, вывода, архитектуру фон-Неймана, гарвардскую архитектуру и многопроцессорные системы. Приводятся примеры построения микроконтроллеров, цифровых процессоров сигналов и процессоров общего назначения.

# 1. Основные положения алгебры логики

Используемые в цифровой технике сигналы близки по форме к прямоугольным и имеют два фиксированных уровня:

| низкий  | 0 – для положительной логики,<br>1 – для отрицательной логики |  |

|---------|---------------------------------------------------------------|--|

| высокий | 1 – для положительной логики,<br>0 – для отрицательной логики |  |

Математическим аппаратом анализа и синтеза цифровых систем служит алгебра логики (булева алгебра – по имени создателя Дж. Буля).

Алгебра логики – это алгебра состояний, а не чисел. Любое логическое выражение, любая логическая функция

$$y = f(x_{n-1}, ..., x_1, x_0)$$

принимает только два значения

$$y = 0$$

, 1 (ложь – истина, да – нет),

точно так же, как и аргументы

$$x_{n-1}, ..., x_1, x_0 = 0, 1$$

(ложь – истина, да – нет).

В основе алгебры логики лежат три основные операции:

1) логическое сложение (дизъюнкция, ИЛИ)

$$y = x_{n-1} + ... + x_1 + x_0 \equiv x_{n-1} \vee ... \vee x_1 \vee x_0$$

(рис. 1.1);

Рис. 1.1. Элемент ИЛИ

Рис. 1.2. Элемент И

2) логическое умножение (конъюнкция, И)

$$y = x_{n-1} \cdot ... \cdot x_1 \cdot x_0 \equiv x_{n-1} \wedge ... \wedge x_1 \wedge x_0$$

(puc. 1.2);

3) инверсия (отрицание, НЕ), рис. 1.3.

Рис. 1.3. Элемент НЕ

Операции И, ИЛИ и НЕ в совокупности образуют *погический базис*. С его помощью можно представить любое сколь угодно сложное логическое выражение. Есть две формы этого представления:

- совершенная дизъюнктивная (СДНФ) и

- совершенная конъюнктивная (СКНФ) нормальные формы.

При составлении СДНФ сначала задаются все значения  $y = y_i$  и соответствующие им комбинации значений аргументов  $(x_{n-1}, ..., x_1, x_0)_i$ :

$$(x_{n-1}, ..., x_1, x_0)_i \rightarrow y_i;$$

$x_i, y_i = 0$  или 1.

Сделать это можно в виде таблицы, которую называют *таблицей истинности*. Примером может послужить таблица 1.1 для некоторой произвольной функции  $y = f(x_0, x_1, x_2, x_3)$  четырех переменных.

Затем по всем возможным комбинациям значений аргументов по приведенным ниже правилам составляются сначала конъюнкции  $K_i$ , затем их произведения  $y_i \cdot K_i$  с требуемыми значениями  $y = y_i$ :

| Таблица 1.1 |       |                 |       |       |                                                                                                                                |  |  |

|-------------|-------|-----------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| y           | $x_3$ | $\mathcal{X}_2$ | $x_1$ | $x_0$ | $y_0 \cdot K_0 \leftarrow \underline{x_{n-1}} \cdot \underline{x_{n-2}} \cdot \dots \cdot \underline{x_1} \cdot x_0 = K_0;$    |  |  |

| 1           | 0     | 0               | 0     | 0     | $y_1 \cdot K_1 \leftarrow x_{n-1} \cdot x_{n-2} \cdot \dots \cdot x_1 \cdot x_0 = K_1;$                                        |  |  |

| 0           | 0     | 0               | 0     | 1     | <u>—————————————————————————————————————</u>                                                                                   |  |  |

| 1           | 0     | 0               | 1     | 0     | $y_2 \cdot K_2 \qquad \leftarrow x_{n-1} \cdot x_{n-2} \cdot \ldots \cdot x_1 \cdot x_0 = K_2;$                                |  |  |

| 1           | 0     | 0<br>0<br>0     | 1     | 1     | <b>:</b>                                                                                                                       |  |  |

| :           | :     | :<br>1<br>1     | ÷     | :     | $y_{2^{n}-2} \cdot K_{2^{n}-2} \leftarrow x_{n-1} \cdot x_{n-2} \cdot \dots \cdot x_{1} \cdot \overline{x_{0}} = K_{2^{n}-2};$ |  |  |

| 0           | 1     | 1               | 1     | 0     |                                                                                                                                |  |  |

| 1           | 1     | 1               | 1     | 1     | $y_{2^{n}-1} \cdot K_{2^{n}-1} \leftarrow x_{n-1} \cdot x_{n-2} \cdot \dots \cdot x_1 \cdot x_0 = K_{2^{n}-1}.$                |  |  |

В  $K_i$  табличным значениям  $x_i = 0$  соответствуют  $\bar{x}_i$  ( $\bar{x}_i \to x_i = 0$ ), а значениям  $x_i = 1 \to x_i$ . Конъюнкции  $K_i$  называют *минтермами*. Их общее число равно  $2^n$  числу возможных комбинаций двоичного кода  $x_{n-1}, x_{n-2}, ..., x_1, x_0$ . СДНФ получается после логического сложения всех полученных произведений:

$$y = \sum_{i=0}^{2^{n}-1} y_{i} \cdot K_{i} \equiv \bigcup_{i=0}^{2^{n}-1} y_{i} \wedge K_{i}.$$

(1.1)

Аналогичным образом составляется СКНФ, но заменой конъюнкций  $K_i$  на дизъюнкции  $D_i$ , называемые *макстермами*. Макстермы  $D_i$  суммируются с соответствующими значениями  $y = y_i$  и полученные после сложений результаты логически перемножаются:

$$y = \prod_{i=0}^{2^{n}-1} (y_{i} + D_{i}) \equiv \bigcap_{i=0}^{2^{n}-1} (y_{i} \vee D_{i}).$$

(1.2)

Здесь

$$\begin{split} D_0 &= \overline{x}_{n-1} \vee \overline{x}_{n-2} \vee ... \vee \overline{x}_1 \vee \overline{x}_0; \\ D_1 &= \overline{x}_{n-1} \vee \overline{x}_{n-2} \vee ... \vee \overline{x}_1 \vee x_0; \end{split}$$

$$D_{2} = \overline{x}_{n-1} \vee \overline{x}_{n-2} \vee ... \vee x_{1} \vee \overline{x}_{0};$$

$$\vdots$$

$$D_{2^{n}-1} = x_{n-1} \vee x_{n-2} \vee x_{1} \vee ... \vee x_{1} \vee x_{0}.$$

функций Схемная реализация логических всегда предполагает минимизацию соответствующих логических выражений. При ЭТОМ уменьшается число логических операций и, как следствие, уменьшаются аппаратные затраты. Для минимизации логических выражений используются аксиомы и законы алгебры логики. Они достаточно очевидны и потому ограничимся их простым перечислением.

Аксиомы 1)  $(\overline{x}) = x;$  6)  $x \wedge 0 = 0;$  2)  $x \vee 0 = x;$  7)  $x \wedge 1 = x;$  8)  $x \wedge x = x;$  4)  $x \vee x = x;$  9)  $x \wedge \overline{x} = 0.$  5)  $x \vee \overline{x} = 1;$

#### Законы

1) Переместительный (закон коммутативности):

$$x \lor y = y \lor x;$$

$x \land y = y \land x;$

2) Сочетательный (закон ассоциативности):

$$x \lor y \lor z = (y \lor x) \lor z = x \lor (y \lor z);$$

$x \land y \land z = (y \land x) \land z = x \land (y \land z).$

3) Распределительный (закон дистрибутивности):

$$x \wedge (y \vee z) = (y \wedge x) \vee (x \wedge z);$$

(или  $x \cdot (y+z) = (y \cdot x) + (x \cdot z)$ ).

В качестве примера рассмотрим функцию двух переменных – функцию равнозначности (эквивалентности)

$$y = x_0 \sim x_1. {(1.3)}$$

Таблица 1.2

| $x_1, x_0$ | y         | Минтермы                                    | Макстермы                               |

|------------|-----------|---------------------------------------------|-----------------------------------------|

| 0, 0       | $y_0 = 1$ | $K_0 = \overline{x}_1 \cdot \overline{x}_0$ | $D_0 = \overline{x}_1 + \overline{x}_0$ |

| 0, 1       | $y_1 = 0$ | $K_1 = \overline{x}_1 \cdot x_0$            | $D_1 = \overline{x}_1 + x_0$            |

| 1, 0       | $y_2 = 0$ | $K_2 = x_1 \ \overline{x}_0$                | $D_2 = x_1 + \overline{x}_0$            |

| 1, 1       | $y_3 = 1$ | $K_3 = x_1 \cdot x_0$                       | $D_3 = x_1 + x_0$                       |

Составим ее СДНФ и СКНФ, а затем минимизируем полученные выражения. Минимизированные выражения называются соответственно минимальной дизъюнктивной (МКНФ) и минимальной конъюнктивной (МКНФ) формами. В

общем случае вид МНДФ и МНКФ различен, но не исключается и их совпадение. Таблица истинности для функции (1.3) представлена в таблице 1.2. В таблице 1.2 помимо значений функции у приведены выражения для всех ее минтермов и макстермов.

При переходе от табличного представления к алгебраическому каждому набору значений переменных в соответствие ставится либо минтерм, либо макстерм.

СДНФ для функции (1.3) равна

$$y = (y_0 \cdot K_0) + (y_1 \cdot K_1) + (y_2 \cdot K_2) + (y_3 \cdot K_3) =$$

$$= 1 (\bar{x}_0 \ \bar{x}_1) + 0 (\bar{x}_0 \ x_1) + 0 (x_0 \ \bar{x}_1) + 1 (x_0 \ x_1),$$

и ей соответствует МНДФ

$$y = x_0 x_1 + \bar{x}_0 \ \bar{x}_1. \tag{1.4}$$

Другая алгебраическая форма представления функции (СКНФ) получается при использовании макстермов:

$$y = (y_0 + D_0)(y_1 + D_1)(y_2 + D_2)(y_3 + D_3) =$$

$$= (1 + \overline{x}_1 + \overline{x}_0)(0 + \overline{x}_1 + x_0)(0 + x_1 + \overline{x}_0)(1 + x_1 + x_0) = (\overline{x}_1 + x_0)(x_1 + \overline{x}_0) =$$

$$= x_1 \cdot \overline{x}_1 + \overline{x}_1 \cdot \overline{x}_0 + x_0 \cdot x_1 + x_0 \cdot \overline{x}_0 = x_0 \cdot x_1 + \overline{x}_0 \cdot \overline{x}_1.$$

Получающееся из нее минимизированное выражение также равно (1.4), что лишний раз подчеркивает равноправность обеих форм представления логических функций.

Как уже говорилось, любую логическую функцию можно представить как совокупность простейших операций логического базиса И, ИЛИ и НЕ. Но наряду с уже перечисленными законами алгебры логики важную роль играет закон инверсии для логических операций сложения и умножения, который известен как теорема де Моргана:

$$\overline{x \vee y \vee z} = \overline{x} \cdot \overline{y} \cdot \overline{z};$$

$$\overline{x \cdot y \cdot z} = \overline{x} \vee \overline{y} \vee \overline{z}.$$

(1.5)

Из этой теоремы следует, что всегда операцию И можно заместить операцией ИЛИ и наоборот, если изменить тип логики и перейти от логики положительной к логике отрицательной. По этой причине наряду с логическим базисом существует понятие *минимального логического базиса*, в основе которого лежат либо операции И и НЕ, либо операции ИЛИ и НЕ.

# 2. Схемотехническая реализация логических операций и функций

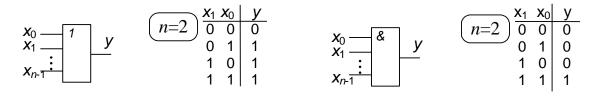

Рассмотрим наиболее часто используемые на практике логические узлы. К ним относятся как простые логические элементы, выполняющие основные операции И, ИЛИ и НЕ, так и более сложные функциональные блоки. Первоначально остановимся на относительно сложных функциях дешифрации и мультиплексирования. Связано это с тем, что названные функции позволяют наиболее простыми средствами реализовать СДНФ.

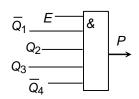

#### 2.1. Полный дешифратор

Функции дешифрования, как и шифровальные функции, достаточно разнообразны и определяются конкретными приложениями. Здесь рассмотрим так называемый *полный дешифратор* (рис. 2.1) – устройство, реализующее весь набор минтермов от n переменных. Выходные сигналы полного дешифратора  $F_i = K_i$  ( $i = 0, 1, ..., 2^n - 1$ ):

Рис. 2.1. Схемное обозначение дешифратора

$$F_0 = \overline{x_{n-1}} \cdot \dots \cdot \overline{x_1} \cdot \overline{x_0} = K_0$$

— на всех входах «0»;  $F_1 = \overline{x_{n-1}} \cdot \dots \cdot \overline{x_1} \cdot x_0 = K_1$  — только  $x_0 = 1$ ;  $F_2 = \overline{x_{n-1}} \cdot \dots \cdot x_1 \cdot \overline{x_0} = K_2$  — только  $x_1$  равен 1;  $\vdots$   $F_{2^n-1} = x_{n-1} \cdot \dots \cdot x_1 \cdot x_0 = K_{2^n-2}$  — все  $x_i$  равны 1.

Полный дешифратор можно рассматривать как преобразователь двоичного кода

$$(x_{n-1},...,x_1,x_0) \rightarrow x_{n-1}\cdot 2^{n-1} + x_{n-2}\cdot 2^{n-1} + ... + x_1\cdot 2^1 + x_0\cdot 2^0$$

(n -разрядность двоичного кода) в унитарный, в котором значение только одного разряда отлично от нуля, а все остальные равны нулю.

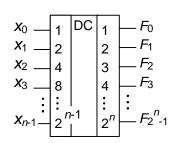

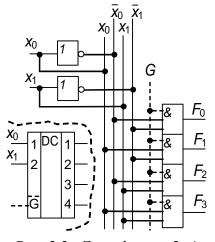

Для полного дешифратора необходимы n логических элементов НЕ и  $2^n$  n-входовых (nИ) элементов И. В качестве примера на рис. 2.2 показана логическая схема полного дешифратора  $2\times4$ .

Функциональные возможности дешифратора можно расширить, если во все элементы И добавить по одному -(n+1)-му - входу, соединив его с общим управляющим

Рис. 2.2. Дешифратор 2×4

входом G. Тогда выходные функции дешифратора будут равны

$$F_i = G \cdot K_i. \tag{2.1}$$

В этом случае на выходах  $F_i$  будет результат дешифрации только при условии G = 1. Если G = 0, то всегда и на всех выходах будут логические нули. Такое устройство относится к классу *стробируемых дешифраторов*.

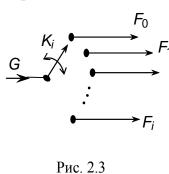

Логическим выражением (2.1) можно описать работу еще одного устройства. Если вход G принять за информационный, а двоичный код ( $x_{n-1}$ , ...,  $x_1$ ,  $x_0$ ) считать кодом переключения выходов (рис. 2.3), то получаем устройство, функция которого состоит в передаче цифровых сигналов по одному из нескольких задаваемых кодом ( $x_{n-1}$ , ...,  $x_1$ ,  $x_0$ ) направлений. Это функция *демультиплексора*, являющегося разновидностью коммутаторов цифровых сигналов.

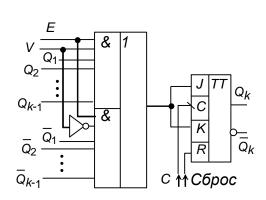

#### 2.2. Мультиплексор

Рис. 2.4. Мультиплексор

Если судить по названию, то мультиплексор также выполняет функцию коммутации, противоположную той, свойственна которая демультиплексору. Однако сначала рассмотрим мультиплексор с другой позиции – с точки зрения логики его работы. Подаваемые на мультиплексор (рис. 2.4) сигналы разбиты на две группы. Одна из них образована варьируемыми комбинациями двоичного кода

$$(x_{n-1}, ..., x_1, x_0)_i$$

;  $i = 0, 1, ..., 2^n - 1$ .

Другая — фиксированной комбинацией значений  $y_2^n$ , ...,  $y_1$ ,  $y_0$ , устанавливаемой на входах  $D_i$  (i = 0, 1, ..., 1, ...)

$2^{n}-1$ ). По каждой из комбинаций  $(x_{n-1}, ..., x_{1}, x_{0})_{i}$  образуются минтермы  $K_{i}$ , которые перемножаются с соответствующими по i значениями  $y_{i}$ . После логического сложения всех произведений образуется СДНФ (1.1) функции  $y=f(x_{n-1}, ..., x_{1}, x_{0})$  n переменных. Вид этой функции определяется задаваемой заранее комбинацией  $(y_{2}^{n}, ..., y_{1}, y_{0})$ . В этом состоит одно из предназначений мультиплексора как функционального блока, реализующего СДНФ функции n переменных.

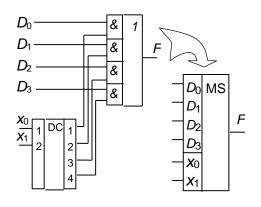

В соответствии с (1.1) логическая схема мультиплексора включает  $2^n$  2-входовых элементов И (элементов 2И), один  $2^n$ -входовый элемент ИЛИ (элемент  $2^n$ ИЛИ) и полный дешифратор  $n \times (2^n)$ . Для примера на рис. 2.5 приведена логическая схема мультиплексора, реализующего функцию  $y = f(x_1, x_0)$  двух переменных, и показано его схемное обозначение.

Рис. 2.6. Пояснение функции мультиплексора

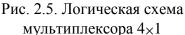

Как уже упоминалось, другим предназначением мультиплексора, которое и определило его название, является коммутация

цифровых сигналов (данных  $D_i$ ), идущих от n источников, на одну информационную линию F (рис. 2.6). В этом случае сигналы на входах  $x_{n-1}, ..., x_1, x_0$  являются сигналами выбора одного из входов  $D_2^{n-1}, ..., D_1, D_0$ , на которые поступают передаваемые данные.

#### 2.3. Схемотехника базовых логических операций

Рассмотренные выше функциональные блоки (мультиплексор и демультиплексор) относительно сложны. Их работа представлена лишь логическими схемами без указания на физическую реализацию. На более низком уровне работа сложных логических узлов описывается посредством простейших операций (операций И, ИЛИ и НЕ), на которые распадаются выполняемые этими узлами функции. Схемотехнический уровень — это самый низкий уровень описания цифровых устройств, на основании которого выполняется их техническая, или, как еще говорят, аппаратная реализация.

Существуют разные технологические решения и варианты цифровых интегральных схем (ИС). Однако в общем случае логические элементы строятся по схеме, состоящей из двух частей или ступеней:

- 1) цепей, выполняющих логические операции;

- 2) цепей согласования логических ступеней с внешней (подключаемой к логическим элементам) нагрузкой.

Сначала остановимся на той части ИС, которая предназначена для выполнения операций дизъюнкции и конъюнкции.

# 2.3.1. Диодные дизъюнкторы

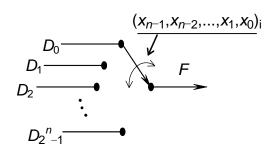

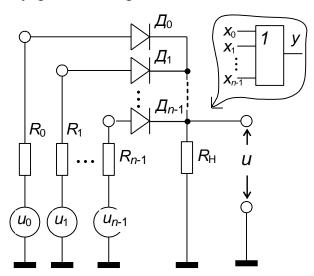

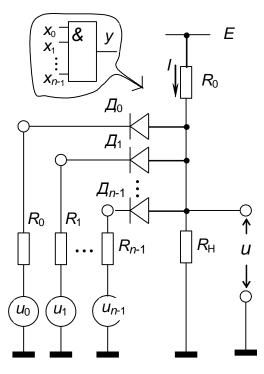

Схема диодного дизъюнктора состоит из развязывающих диодов  $\mathcal{L}_i$  (i = 0, 1, ..., n-1; n – число входов) и нагрузочного сопротивления  $R_H$  (рис. 2.7).

Резисторы  $R_0$ ,  $R_1$ , ...,  $R_{n-1}$  не являются функционально необходимыми и представляют внутренние сопротивления диодов. Обычно источники сигналов  $u_0$ ,  $u_1$ , ...,  $u_{n-1}$  имеют малые внутренние сопротивления. Если это не так, то их внутренние сопротивления можно включить в  $R_0$ ,  $R_1$ , ...,  $R_{n-1}$ .

Рис. 2.7. Диодный дизъюнктор

Напряжения  $u_0$ ,  $u_1$ ,...,  $u_{n-1}$  соответствуют входным переменным  $x_0$ ,  $x_1$ ,...,

$x_{n-1}$ , а напряжение u – выходной переменной у логического элемента:

$$u_0 \rightarrow x_0, u_1 \rightarrow x_1, ..., u_{n-1} \rightarrow x_{n-1};$$

$u \rightarrow y.$

В положительной логике

Высокому  $U^{+}$  и низкому  $U^{-}$  уровням напряжений соответствуют логическая

единица и логический нуль. При этом высокий уровень выходного напряжения u не должен зависеть от сопротивлений  $R_0$ ,  $R_1$ ,...,  $R_{n-1}$ . Поэтому их величины должны быть значительно меньше сопротивления нагрузки:

$$R_0, R_1, ..., R_{n-1} \ll R_H.$$

Тогда появление на любом из входов (или на любой группе входов) высокого уровня  $U^+$  приводит к возникновению тока через соответствующий диод (или группу диодов) и выходное напряжение будет примерно равно высокому уровню  $U^+$  ( $u \approx U^+$ ), соответствуя y = 1. Таким образом в положительной логике выполняется операция логического сложения (операция nИЛИ)

$$y = x_{n-1} \vee ... \vee x_1 \vee x_0.$$

Однако если перейти *от логики положительной к логике отрицательной*, то представленная на рис. 2.7 схема будет выполнять операцию конъюнкции. Действительно, только в том случае, когда на всех входах  $u_0$ ,  $u_1$ , ...,  $u_{n-1}$  присутствует низкий уровень напряжения (на всех входах — логические «1»), все диоды  $\mathcal{I}_i$  закрыты и на выходе будет низкий уровень напряжения, то есть логическая «1». Во всех остальных случаях на выходе будет логический «0». Следовательно, в отрицательной логике реализуется функция И ( $y = x_{n-1} \wedge ... \wedge x_1 \wedge x_0$ ). Такая двойственность одного логического элемента в алгебре логики сформулирована как теорема де Моргана (см. соотношения (1.5)) и потому имеет характер общей закономерности, означающей, что любой базовый логический элемент (И или ИЛИ) в зависимости от типа логики можно

использовать как элемент И/ИЛИ (И — в положительной, ИЛИ — в отрицательной логике) или ИЛИ/И (ИЛИ — в положительной, И — в отрицательной логике).

#### 2.3.2. Диодные конъюнкторы

Рис. 2.8. Диодный конъюнктор

Диодный конъюнктор (рис. 2.8), как и дизъюнктор, своем составе имеет развязывающие (или, как еще говорят, фазоразделительные) диоды  $\mathcal{I}_i$  (i = 0,1,...,n-1) и нагрузочный резистор  $R_{\rm H}$ . Ток через резистор  $R_{\rm H}$  зависит от того, как ток I источника напряжения питания E распределяется между нагрузкой и диодами. Как и прежде, резисторы  $R_0$ ,  $R_1$ , ...,  $R_{n-1}$  представляют внутренние сопротивления диодов и источников входных сигналов и потому желательно, чтобы их величины не были значительными:

$$R_0, R_1, ..., R_{n-1} \ll R_H.$$

В этом случае низкий уровень выходного напряжения не будет зависеть от числа открытых диодов и будет близким к нулю ( $u = U^{-} \approx 0$ ). Снова для начала к рассмотрению примем положительную логику. Диоды

пропускают ток, если

$$u_0 = u_1 = \dots = u_{n-1} = 0 \quad (x_0 = x_1 = \dots = x_{n-1} = 0).$$

При этом напряжение на выходе  $u \approx 0$  и y = 0. Включение высокого уровня  $U^+$  по любому из входов  $u_0$  ...  $u_{n-1}$  не изменит величины u и оставит y = 0 за исключением того случая, когда

$$u_0 = u_1 = \dots = u_{n-1} = U^+ \quad (x_0 = x_1 = \dots = x_{n-1} = 1).$$

(2.2)

При условии (2.2)  $u = U^+$  и y = 1. Следовательно, в положительной логике реализуется операция nИ:  $y = x_{n-1} \wedge ... \wedge x_1 \wedge x_0$ . Отметим еще раз, что смена логики на отрицательную превращает конъюнктор в дизъюнктор. Справедливо это для всех разновидностей логических элементов.

# 2.3.3. Выполнение логических операций с помощью транзисторов

Схемотехническая реализация логических элементов предполагает наличие в том или ином виде электронных ключей, которые могут пребывать в

двух (если не учитывать переходные процессы) состояниях – закрытом и открытом. Подобное имеет место в рассмотренных выше диодных логических узлах. Транзисторные схемы разнообразны не только по своей структуре, но и по используемым в них типам транзисторов. Для построения цифровых интегральных схем в настоящее время по большей части используется кремний (Si), который служит материалом для создания ИС со сверхвысокой степенью интеграции (до и более нескольких десятков миллионов транзисторов на кристалл) сверхвысокой производительностью. Для создания сверхбыстродействующих цифровых устройств применяются также полупроводники группы A<sub>III</sub>B<sub>v</sub>, в частности арсенид галлия (GaAs), однако уровень интеграции таких ИС не выше средней (до нескольких сотен транзисторов на кристалл).

Основные разновидности применяемых в цифровых ИС транзисторов представлены в таблице 2.1. Интегральные схемы, как правило, имеют планарную структуру, и ее элементы получаются на поверхности полупроводника методами литографии (для кремниевых приборов) или молекулярно-лучевой эпитаксии (для GaAs-приборов). Отсюда происходит используемый в таблице термин «подложка».

Выделим сначала группу кремниевых приборов, в основе работы которых лежат контакты полупроводников с разным типом проводимости — электронной n и дырочной p. Это биполярные (p-n-p) или n-p-n, а также полевые с управляющим p-n-переходом транзисторы.

С точки зрения применений основное отличие биполярных транзисторов от полевых заключается в том, что биполярные транзисторы — это приборы, управляемые током, а полевые — приборы, управляемые напряжением (что отражено в названии «полевые»). Это значит, что сопротивление входов логических элементов на биполярных транзисторах значительно ниже, чем у элементов на полевых транзисторах. Последнее накладывает свой отпечаток как на техническую реализацию логических операций, так и на способы согласования одних элементов с другими.

Полевые транзисторы с управляющим p-n-переходом подразделяются по типу проводимости канала: имеются транзисторы с n-каналом (p-затвором) и транзисторы с p-каналом (n-затвором).

У полевых транзисторов на арсениде галлия управляющим является барьер Шоттки — переход металл—полупроводник. Канал транзистора — это примыкающая к металлическому затвору область полупроводника, по обе стороны от которой расположены исток и сток. Такая структура транзистора нашла отражение в его названии МЕП(металл—полупроводник)-транзистор.

<sup>&</sup>lt;sup>1</sup> Управляющим напряжением для биполярных транзисторов является разность потенциалов между базой и эмиттером, а для полевых – между затвором и истоком.

# Разновидности и схемные обозначения транзисторов

|                                         | Полевые транзисторы                                                                                                               |                                            |                                                        |  |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------|--|--|

| Биполярные                              | С управляющим <i>p-n</i> -переходом и                                                                                             | С изолированным затвором (МДП-транзисторы) |                                                        |  |  |

| транзисторы                             | транзисторы                                                                                                                       | С встроенным каналом                       | С индуцированным                                       |  |  |

|                                         | с барьером Шоттки                                                                                                                 | (нормально открытые                        | каналом ( <i>нормально</i>                             |  |  |

|                                         | (МЕП-транзисторы)                                                                                                                 | транзисторы)                               | закрытые транзисторы)                                  |  |  |

| б к<br>n-p-n<br>э                       | $rac{3}{u}$ $rac{c}{u}$ $n$ -канал                                                                                                | з                                          | <b>з</b>                                               |  |  |

| б к<br>р-п-р                            | u $v$ $u$ $u$ $v$ $u$ | <b>з</b>                                   | <b>з</b> ј <mark>с р</mark> -канал,<br>п-подложка<br>и |  |  |

| э - эмиттер                             | <i>u</i> - исток                                                                                                                  | <i>u</i> - исток                           | <i>u</i> - исток                                       |  |  |

| <i>к</i> - коллектор<br><i>б</i> - база | <i>С -</i> сток<br>3 - затвор                                                                                                     | <i>С</i> - сток<br>3 - затвор              | С - сток<br>3 - затвор                                 |  |  |

$<sup>^{*)}</sup>$  МЕП-транзисторы имеют только  $\emph{n}\text{-}$ каналы.

В цифровых интегральных схемах широко применяются транзисторы с изолированным, то есть отделенным от канала слоем диэлектрика, затвором. Образованная таким образом структура металл—диэлектрик—полупроводник (МДП) дала название этому типу транзисторов — МДП-транзисторы. Их отличительной особенностью является высокое сопротивление постоянному току со стороны управляющего электрода — затвора. Во всем многообразии применений в интегральной схемотехнике МДП-транзисторы до настоящего времени являются преимущественно кремниевыми приборами. В качестве диэлектрика в МДП-структурах традиционно применялась и применяется двуокись кремния SiO<sub>2</sub>. В таких случаях для обозначения МДП-транзисторов используется аббревиатура МОП (металл—окисел—полупроводник) вместо МДП.

Как и все полевые МДП-транзисторы различаются по типу проводимости канала (p- или n-типу). К этому добавляется еще различие по пороговому напряжению  $U_{\Pi OP}$  на управляющем электроде — затворе, определяющему границу перехода транзистора из закрытого состояния в проводящее. По этому признаку различают транзисторы c встроенным и индуцированным каналами. У транзисторов с встроенным каналом проводимость сток—исток существует при нулевой разности потенциалов между затвором и истоком. Поэтому такой транзистор называют еще нормально открытым. В отличие от нормально открытого, транзистор с индуцированным каналом приобретает приводимость лишь тогда, когда управляющее напряжение на затворе превысит величину порога  $^9$   $U_{\Pi OP}$ . Этим объясняется и называние его как нормально закрытого.

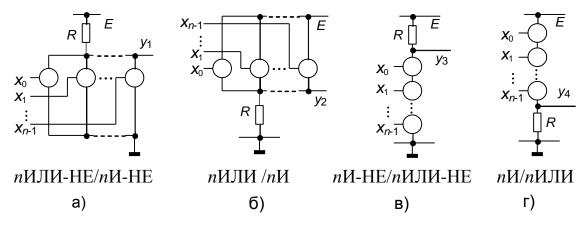

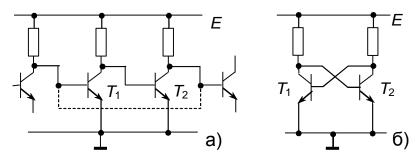

Логические операции можно выполнять, соответствующим образом выстраивая сети ключевых транзисторов. Принцип построения таких сетей достаточно прост и не зависит от типа используемых приборов. В конкретных реализациях, естественно, должны быть учтены физические различия в функционировании электронных приборов и составленных из них цепей. Внешне эти различия проявляются прежде всего в действующих токах и напряжениях. Однако на функциональном уровне схемы, с помощью которых выполняются логические операции, можно представить простейших последователь-ных и параллельных соединений ключевых транзисторов. Использование таких соединений для выполнения базовых логических операций И, ИЛИ, И-НЕ и ИЛИ-НЕ в обобщенном виде показано на рис. 2.9.

В положительной логике параллельное соединение транзисторов дает возможность выполнять операции ИЛИ с инверсией (nИЛИ-НЕ, рис. 2.9а) или без инверсии (nИЛИ, рис. 2.9б). В отрицательной логике те же элементы выполняют операции nИ-НЕ и nИ соответственно. Последовательное соединение транзисторов в положительной/отрицательной логике реализует операции nИ-НЕ/nИЛИ-НЕ (рис. 2.9в) или nИ/nИЛИ (рис. 2.9г).

148

\_

$<sup>^{9}</sup>$  Для транзисторов с разной проводимостью каналов  $U_{\it \Pi OP}$  имеет разные знаки.

Рис. 2.9. Схема построения логических элементов на ключевых транзисторах

#### 2.3.4. Диодно-транзисторная логика

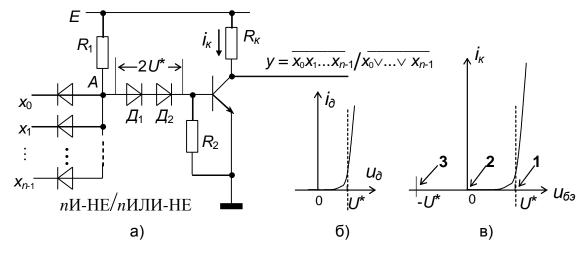

Как уже упоминалось выше, в общем случае логические элементы в своем составе имеют цепи, отвечающие за выполнение логических операций, и выходные цепи, служащие для согласования выхода одного элемента с входами других. В диодно-транзисторной логике (ДТЛ) для выполнения логических операций используются диодные конъюнкторы или дизъюнкторы, а в качестве согласующих цепей — простые или сложные инверторы. Один из таких элементов (элемент *п*И-НЕ/*п*ИЛИ-НЕ) представлен на рис. 2.10. В нем логический узел выполнен как диодный конъюнктор, а согласующим (выходным) каскадом является простой инвертор, выполненный по схеме с общим эмиттером. В дальнейшем, чтобы избежсать повторений, логические элементы будем классифицировать по операциям в положительной логике, не делая напоминаний о том, как меняется их функция при смене логики на отрицательную.

Рис. 2.10. Элемент диодно-транзисторной логики, выполненный по гибридноинтегральной технологии (а) и вольт-амперные характеристики кремниевого диода (б) и кремниевого биполярного транзистора (в)

Если на каком-то одном или нескольких входах логического элемента на рис. 2.10  $x_i = 0$ , то один или несколько фазоразделительных диодов будут в проводящем состоянии и напряжение  $u_A$  в точке их соединения (рис. 2.10a, точка A) будет равно напряжению на открытом p-n-переходе  $U^*$ . Кремниевый p-n-переход отличен тем, что ток диода  $i_{\partial}$  в прямом направлении начинает заметно расти только тогда, когда напряжение на диоде  $u_{\partial}$  достигнет величины  $u_{\partial} = U^*$  (рис. 2.10б). После этого с увеличением  $u_{\partial}$  ток  $i_{\partial}$  растет настолько быстро, что напряжение на открытом p-n переходе можно считать почти постоянным и примерно равным  $U^*$  ( $u_0 \approx U^*$ ). При этом на открытом переходе диапазон изменений  $u_{\partial}$  незначителен и составляет величину  $\Delta u_{\partial} \approx (0,1...0,2)$  В, в то время как  $U^* \approx (0.65...0.7)$  В. Поэтому напряжение на открытом переходе  $u_{\partial}$  $\approx U^*$  называют еще «напряжением пятки», или просто «пяткой». Подобными свойствами обладают также эмиттерный и коллекторный *p-n*-переходы кремниевого транзистора. Это значит, что транзистор в открытое состояние переходит лишь тогда, когда управляющее напряжение между базой и эмиттером  $u_{\tilde{n}_2} > U^*$ .

Помимо развязывающих диодов в схеме логического элемента имеются два дополнительных диода  $\mathcal{J}_1$  и  $\mathcal{J}_2$ . С их помощью повышается помехозащищенность логического элемента. В подтверждение этого рассмотрим три схемных решения.

- 1) Развязывающие диоды соединены с базой транзистора непосредственно. Помехи наиболее опасны, когда среди всех сигналов  $x_i$  есть  $x_i = 0$ . В этом случае напряжение  $u_A$  в общей для диодов точке A, а значит, и разность потенциалов между базой и эмиттером  $u_{69}$ , равны примерно  $U^*$  (рис. 2.10в, точка 1). Ток через транзистор минимален (близок к нулю) и плохо контролируем.

- 2) Развязывающие диоды соединены с базой через один диод (например, только через  $\mathcal{I}_1$ ). В этом случае по-прежнему при одном или нескольких  $x_i = 0$   $u_A \approx U^*$ , но  $u_{\delta 9} \approx u_A U^* \approx 0$  (рис. 2.10в, точка 2). Транзистор инвертора закрыт.

- 3) Развязывающие диоды соединены с базой через два диода (Д<sub>1</sub> и Д<sub>2</sub>). Надежность закрытого состояния транзистора повышена за счет того, что при  $x_i = 0$   $u_{\tilde{0}3} \approx u_A 2U^* \approx -U^*$  (рис. 2.10в, точка 3).

Исторически сложилось так, что термин «*диодно-транзисторная логика*» – ДТЛ используется применительно к одним из самых первых логических элементов, выполненных по гибридно-интегральной технологии. Однако здесь для общности рассмотрения термином ДТЛ будем пользоваться в отношении тех логических элементов, в которых логические операции выполняются с помощью диодов, а функции согласования возложены на транзисторы.

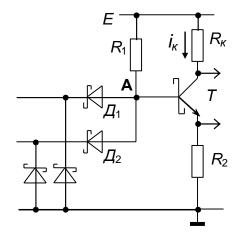

Другой пример построения диодно-транзисторной логики представлен на рис. 2.11. Логический узел этих кремниевых приборов выполнен на диодах Шоттки (диоды  $\mathcal{L}_1$  и  $\mathcal{L}_2$ ). Барьер Шоттки имеет более высокую скорость

переключения по сравнению с р-п-переходом, что обеспечивает повышенное логического элемента. быстродействие В выходных применяются диоды Шоттки. Подключаются они параллельно коллекторному переходу (транзистор T на рис. 2.11) в наиболее ответственных участках схемы и предохраняют транзистор от попадания в режим глубокого насыщения. Происходит это потому, что при переходе в открытое состояние барьер Шоттки начинает проводить ток раньше, чем коллекторный переход транзисторного ключа. Тем самым сокращается время переключения транзистора из открытого состояния в закрытое и повышается быстродействие логического элемента. Транзисторы с параллельным коллекторному переходу барьером Шоттки называют транзисторами Шоттки. В схемах ДЛЯ них используется специальное (такое, как для транзистора T на рис. 2.11) обозначение.

Логический элемент на рис. 2.11 по входам защищен от отрицательных выбросов напряжения соединенными с линией нулевого потенциала (с «землей») диодами Шоттки, что также способствует повышению быстродействия.

Рис. 2.11. Фрагмент элемента 2И-НЕ/2ИЛИ-НЕ с барьерами Шоттки

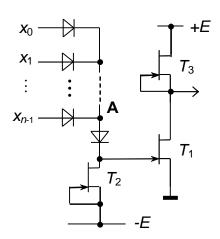

Рис. 2.12. Базовый элемент диоднополевой логики

По диодно-транзисторной схеме строятся не только кремниевые, но и сверхбыстродействующие GaAs логические элементы. На рис. 2.12 показан базовый элемент диодно-полевой логики (ДПЛ), в котором фазоразделительные диоды выполнены как барьер Шоттки; ключевой  $T_1$  и нагрузочные  $T_2$  и  $T_3$ транзисторы – МЕП-транзисторы. Транзисторы  $T_2$  и  $T_3$ , у которых затворы соединены с истоком, выполняют функцию резисторов, но в отличие от являются не постоянной, а динамической (зависящей приложенного напряжения) нагрузкой для протекающего через них тока. Замена резисторов на динамическую нагрузку позволяет упростить процесс изготовления ИС элементов логики и понизить вольтность источников питания. Более подробно эти вопросы обсудим при рассмотрении логических элементов на транзисторах с изолированным затвором.

#### 2.3.5. Транзисторно-транзисторная логика

Для логических операций удобно использовать многоэмиттерные и многоколлекторные транзисторы. Рассмотрим сначала группу элементов, в которой логические узлы выполнены как многоэмиттерные транзисторы — это группа *транзисторно-транзисторной логики* (ТТЛ) (рис. 2.13). Принцип выполнения в ней логических операций исходит из диодной логики. Однако если диодные *p-n*-переходы работают автономно, то в многоэмиттерном транзисторе они имеют общую базу, каковой является база транзистора.

Рис. 2.13. Базовый элемент ТТЛ с расширением по ИЛИ

Если на каком-либо эмиттере транзистора  $T_1$  присутствует низкий уровень напряжения, то соответствующий эмиттерный переход открыт и коллекторный ток транзистора  $T_1$  течет в сторону от базы транзистора  $T_2$ , переводя последний в закрытое состояние. При этом транзистор  $T_3$  открыт, а транзистор  $T_4$  закрыт и на выходе присутствует высокий уровень напряжения. Если на всех входах  $x_i$  равны единице, то  $T_1$  оказывается в инверсном включении, то есть в состоянии с закрытыми эмиттерными и открытым коллекторным переходами. В этом случае ток от  $T_1$  течет в сторону базы транзистора  $T_2$  и открывает его. При этом на коллекторе  $T_2$  возникает отрицательное напряжение, а на эмиттере — положительное, что приводит к закрыванию  $T_3$  и открыванию  $T_4$ . Как следствие, на выходе логического элемента будет низкий уровень напряжения. Таким образом выполняется логическая операция nИ-HE.

Диод, стоящий в последней ступени выходного каскада, смещает вниз (к нулю) низкий уровень выходного сигнала, обеспечивая его соответствие уровням входных сигналов в транзисторно-транзисторной логике, что необходимо для соединений одних элементов с другими.

Отметим еще одну особенность ТТЛ. Если в промежуточной секции выходного каскада вместо одного транзистора  $T_2$  применять несколько параллельно соединенных, то дополнительно реализуется операция

логического сложения (операция ИЛИ) так, как это показано на рис. 2.9. Число слагаемых определяется числом параллельных транзисторов. Таким образом получаются логические элементы U с расширением по UЛИ. На рис. 2.13 показано расширение с двумя параллельными транзисторами  $T_2$  и  $T_5$ . При каждом из них имеется свой логический узел, и это в совокупности дает операцию И-ИЛИ-НЕ.

Столь удачная реализация операций И/ИЛИ дала начало обширному семейству схем ТТЛ. Появились они в 1968 г., а через 15 лет составляли более 50% общего объема всех цифровых ИС, производимых в мире.

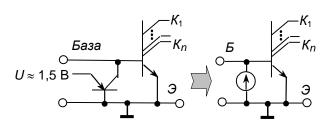

#### 2.3.6. Интегральная инжекционная логика

Рис. 2.14. Элементарная ячейка инжекционной логики и ее эквивалентная схема

В интегральной инжекционной логике ( $H^2\Pi$ ) удачно сочетаются *p-n-p*n-p-n-транзисторы. Элементарная ячейка инжекционной логики (рис. 2.14) состоит из инжектора (p-n-pтранзистор) И многоколлекторного ключа (n-p-n-транзистор). Напряжение питания Uподается эмиттер инжектора и составляет около 1,5 В. По

этой причине токи переключения ключевого транзистора относительно невелики, что сказывается на быстродействии элементов  $\mathrm{H}^2\Pi$ . Такая логика, будучи привлекательной с точки зрения технологического решения, употребима лишь в низкоскоростных цифровых устройствах.

Рис. 2.15. Схема выполнения логических операций в интегральной инжекционной логике

#### 2.3.7. Эмиттерно-связанная логика

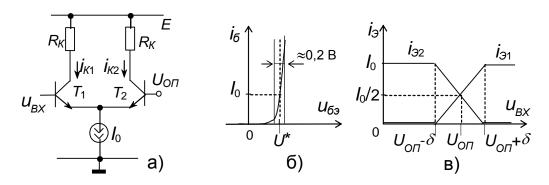

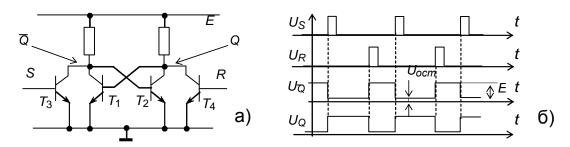

Среди логик на биполярных транзисторах эмиттерно-связанная логика (ЭСЛ) является самой быстродействующей. В основе ее работы лежит переключатель тока (рис. 2.16), транзисторы  $T_1$  и  $T_2$  которого работают в активном режиме, непопадая в режим насыщения. Тем самым увеличивается скорость переключения и быстродействие логических элементов.

На базе  $T_2$  присутствует постоянное опорное напряжение  $U_{OII}$ . Управляющее напряжение подается на базу  $T_1$ . При  $u_{BX} = U_{OII}$  оба транзистора открыты и через каждый из них протекает ток  $I_0/2$ . Потенциалы эмиттеров  $u_{91}$  и  $u_{92}$  одинаковы и равны  $u_9 = U_{OII} - U^*$ , что обеспечивает равенство коллекторных  $(i_{K1}$  и  $i_{K2})$  и эмиттерных токов  $(i_{91}$  и  $i_{92})$ :

$$i_{K1} = \alpha i_{31}$$

;  $i_{K2} = \alpha i_{32}$ ;  $i_{31} = i_{32} = I_0/2$

(рис. 2.16в);  $\alpha \approx 1$  – коэффициент передачи тока эмиттера в коллектор.

Рис. 2.16. Переключатель тока на дифференциальном каскаде

Уменьшение  $u_{BX}$  на величину  $\delta \ge 0,1$  В (рис. 2.16) не изменит потенциала эмиттеров  $u_3$ , поскольку его величина  $u_3 = U_{OII} - U^*$  и поддерживается транзистором  $T_2$ . Это вызывает уменьшение разности потенциалов между базой и эмиттером транзистора  $T_1$  на величину  $\delta$ :

$$u_{E\ni 1} = U^* - \delta$$

.

В результате ток транзистора  $T_1$  в десятки раз уменьшится и будет близок к нулю, в то время как ток транзистора  $T_2$  достигнет максимального значения  $I_0$ :

$$i_{31} \approx 0$$

,  $i_{32} \approx I_0$ .

При повышенном управляющем напряжении  $u_{BX} = U_{OII} + \delta$  открывается транзистор  $T_1$  и в этом случае он будет фиксировать потенциал эмиттеров, что переведет  $T_2$  в закрытое состояние:

$$u_{ij} = U_{OII} - U^* + \delta$$

,  $u_{E32} = U^* - \delta$ ,  $i_{32} \approx 0$  и  $i_{31} \approx I_0$ .

Таким образом, перепад потенциала  $\Delta u_{B1} = \pm \delta$  около средней величины  $U_{OII}$  обеспечивает переключение тока  $I_0$  от одного транзистора к другому.

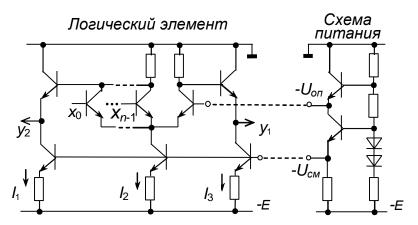

Логические операции в базовом элементе ЭСЛ (рис. 2.17) выполняются за счет параллельного соединения транзисторов в управляемом плече

Рис. 2.17. Базовый элемент ЭСЛ

переключателя тока, что дает операцию ИЛИ. Входные сигналы  $x_0$ ,  $x_1$ , ...,  $x_{n-1}$  подаются на базы управляемых транзисторов. Два выходных каскада, выполненные как эмиттерные повторители, дают противофазные сигналы  $y_1$  и  $y_2$ . При этом

$$y_1 = x_{n-1} \vee ... \vee x_1 \vee x_0$$

(пИЛИ),  $y_2 = \overline{x_{n-1} \vee ... \vee x_1 \vee x_0}$  (пИЛИ-НЕ).

Транзисторы нижнего ряда являются источниками токов  $I_1$ ,  $I_2$  и  $I_3$  для переключателя и выходных каскадов. На рисунке показана также схема, вырабатывающая опорное напряжение  $U_{OH}$  и напряжение смещения  $U_{CM}$  для всех интегрированных в одну ИС логических элементов.

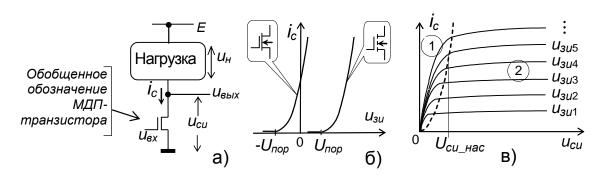

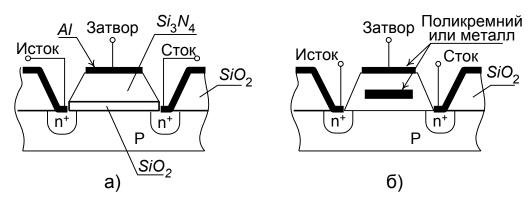

# 2.3.8. МДП-ключи и логика на МДП-структурах

Основными активными компонентами больших (БИС) и сверхбольших (СБИС) интегральных схем являются полевые транзисторы с изолированным затвором (МДП(МОП)-транзисторы). В основе МДП-логики лежит МДП-ключ, обобщенная схема которого без учета свойств канала приведена на рис. 2.18а.

При работе с ключом должны быть учтены характерные особенности ключевого транзистора, в частности, его *статические проходные* (зависимость  $i_C = i_C(u_{3H})$  тока стока  $i_C$  от напряжения затвор–исток  $u_{3H}$ ) и *выходные* (семейство кривых  $i_C = i_C(u_{CH})$ ) характеристики<sup>10</sup>.

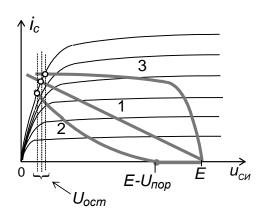

Для режима ключа важно значение порогового напряжения  $U_{\Pi OP}$ , поскольку им определяются высокий  $U^+$  и низкий  $U^-$  уровни управляющего напряжения  $u_{3U}$ , переводящих транзистор в открытое/закрытое состояние. У транзисторов с встроенным каналом  $U_{\Pi OP} < 0$ , а у транзисторов с каналом индуцированным  $U_{\Pi OP} > 0$  (рис. 2.18б). Это отражено и на семействе выходных (рис. 2.18в) характеристик, для которых  $u_{3U}$  является параметром:

$$U_{\Pi OP} < u_{3U1} < u_{3U2} < u_{3U3} < u_{3U4} < u_{3U5} \dots$$

На выходных характеристиках МДП-транзистора (рис. 2.18в) различимы две области: область 1 левее пунктирной кривой, в которой ток стока заметно растет с ростом напряжения сток—исток, и область 2, где ток  $i_C$  определяется в основном управляющим напряжением  $u_{3H}$  и слабо зависит от  $u_{CH}$ . В области 1

$$i_C \approx b \cdot \left[ \left( u_{3H} - U_{\Pi OP} \right) \cdot u_{CH} - \frac{1}{2} u_{CH}^2 \right], \tag{2.3}$$

Рис. 2.18. Обобщенная схема МДП-ключа (a) и статические проходные (б) и выходные (в) вольт-амперные характеристики МДП-транзистора

$b = W\mu C_0/L$  — удельная крутизна; W и L — ширина и длина затвора транзистора,  $\mu$  — подвижность носителей тока (электронов или дырок) в канале,  $C_0 = \varepsilon_{a\_\partial u \ni \pi}/d_{\partial u \ni \pi}$  — удельная емкость затвора,  $\varepsilon_{a\_\partial u \ni \pi}$  — абсолютная диэлектрическая проницаемость,  $d_{\partial u \ni \pi}$  — толщина слоя диэлектрика между затвором и каналом и  $\varepsilon_{a\_\partial u \ni \pi}$  =  $\varepsilon_{\partial u \ni \pi}$ .  $\varepsilon_0$  — где  $\varepsilon_{\partial u \ni \pi}$  — относительная диэлектрическая проницаемость, а  $\varepsilon_0$  — диэлектрическая проницаемость вакуума.

Уравнение (2.3) справедливо при  $u_{CH}$ , не превышающих *напряжения* насыщения  $U_{CH\_HAC}$ . Величина  $U_{CH\_HAC}$  зависит от управляющего напряжения  $u_{3H}$  и равна

\_

$<sup>^{10}</sup>$  Показаны характеристики для транзистора с n-каналом.

$$U_{CH\_HAC} = u_{3H} - U_{\Pi OP}. \tag{2.4}$$

На рис. 2.18в зависимость  $U_{CU\_HAC} = U_{CU\_HAC}(u_{CU})$  отмечена пунктирной кривой, разделяющей области 1 и 2. В области 1  $u_{CH} < U_{CU\_HAC} = u_{3H} - U_{\Pi OP}$ . В области 2  $u_{CH} > U_{CU\_HAC}$  и ток стока определяется его значением при  $u_{CH} = U_{CH}$  $_{\_HAC}$ . При этом аналитически проходные и выходные характеристики транзистора можно описать с помощью выражений:

$$i_C \approx i_C(U_{CU\_HAC}) = i_C(u_{3U} - U_{\Pi OP});$$

$i_C \approx 0.5b(u_{3U} - U_{\Pi OP})^2.$

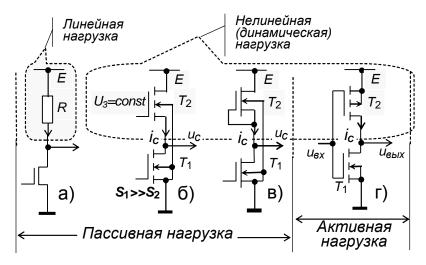

МДП-ключи различают не только по свойствам ключевого транзистора, но и по типу нагрузки. Простейшим является ключ с резистивной нагрузкой  $R_H = R$  (рис. 2.19а). Однако техническое исполнение резистора R требует иных по сравнению с транзисторами технологических операций. Кроме того, на резисторах рассеивается значительная доля энергии источника питания, что неприемлемо для интегральных схем с точки зрения их температурного режима и расходуемой мощности источника питания. Поэтому в ИС используется нелинейная нагрузка, роль которой выполняют транзисторы. Сопротивление транзистора зависит от величины тока в канале, и такая нагрузка является динамической. Есть две основные разновидности нелинейной нагрузки – пассивная и активная. Потенциал затвора в пассивной нагрузке либо фиксирован (рис. 2.19б), либо равен потенциалу истока (рис. 2.19в).

Рис. 2.19. МДП(МОП)-ключи с резистивной нагрузкой (a), на нормально закрытых (б), нормально открытых (в), комплементарных (г) транзисторах

В первом случае (рис. 2.19б) и ключевой  $T_1$ , и нагрузочный  $T_2$  транзисторы являются транзисторами с индуцированным (нормально закрытым) каналом. Как правило, затвор  $T_2$  подключается к источнику питания  $(U_3 = E)$ . Поэтому при высоком уровне потенциала на затворе  $T_1$  открытыми оказываются оба транзистора  $T_1$  и  $T_2$ . Для логических операций необходимо, чтобы низкий уровень напряжения  $U = U_{OCT} (U_{OCT} - \text{ остаточное напряжение на стоке открытого транзистора <math>T_1$ ) был достаточно малым. Это выполняется

тогда, когда внутреннее сопротивление  $R_{i1}$  транзистора  $T_1$  меньше  $R_{i2}$  – внутреннего сопротивления транзистора  $T_2$  ( $R_{i1} < R_{i2}$ ) или, что то же самое, крутизна  $T_1$  больше крутизны  $T_2$  ( $S_1 > S_2$ ). О такой схеме ключа говорят как о схеме с отношением: для транзисторов  $T_1$  и  $T_2$  отношение  $S_1/S_2 \neq 1$ .

Во втором случае (рис. 2.19в) применяются нормально открытые (с встроенным каналом) транзисторы и для обеспечения проводимости канала не требуется повышенного напряжения на затворе. Поэтому затвор нагрузочного транзистора  $T_2$  соединен с истоком.

В процессе переключения состояние ключа можно определить по его динамическим характеристикам (ДХ), в частности по выходной ДХ

$$u_{CH}(i_C) = E - u_H(i_C).$$

(2.5)

При линейной пассивной нагрузке  $R_H = R$  (рис. 2.19а) ДХ имеет вид прямой линии (линия 1 на рис. 2.20), описываемой уравнением  $u_{CH}(i_C) = E - i_C R$ . При динамической нагрузке зависимость (2.5) более. В открытом ключе, построенном на нормально закрытых транзисторах (рис. 19б),  $u_{3H2} > U_{\Pi OP\_2}$  и напряжение  $u_C < U_3 - U_{\Pi OP\_2}$ . Поэтому ток ключа контролируется нагрузочным транзистором и равен

$$i_C = i_{C,2} \approx 0.5b_2(u_{3H,2} - U_{\Pi OP,2})^2 = 0.5b_2(U_3 - u_C - U_{\Pi OP,2})^2,$$

поскольку сопротивление  $R_{i2}$  канала транзистора  $T_2$  значительно больше сопротивления  $R_{i1}$  канала транзистора  $T_1$ . При  $U_3 = E$  это соответствует кривой 2 на рис. 2.20. Динамическая характеристика транзистора  $T_1$  в ключе с нормально открытыми транзисторами (рис. 19в) соответствует инвертированной и смещенной на величину напряжения источника питания E по оси напряжений статической характеристике транзистора  $T_2$  при  $u_{3H_2} = 0$  (кривая 3 на рис. 2.20).

Рис. 2.20. Выходные динамические характеристики МДП-транзистора с резистивной (1) и динамической (2 и 3) нагрузкой (2 – нормально закрытый и 3 – нормально открытый транзисторы)

Рис. 2.21. Динамическая характеристика (пунктирная кривая) транзистора с активной нагрузкой на комплементарном транзисторе

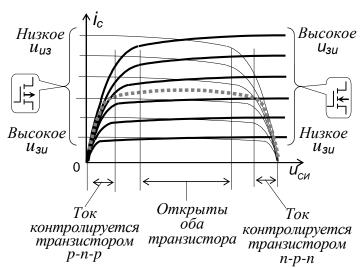

Нелинейная активная нагрузка представляет собой комплементарный транзистор ( $T_2$  на рис. 2.19г), управляемый тем же напряжением, что и транзистор  $T_1$  ( $T_1$  и  $T_2$  – это транзисторы с индуцированным каналом). Стоки  $T_1$  и  $T_2$  соединены вместе, а исток  $T_2$  подключен к источнику питания. При таком включении выходные статические характеристики имеют вид, представленный на рис. 2.21: тонкие сплошные линии – это семейство характеристик p-канального транзистора  $T_2$ , а более толстые сплошные линии – семейство характеристик p-канального транзистора  $T_1$ . Динамическая характеристика имеет вид пунктирной кривой.

В статическом режиме ток  $i_C$  через комплементарный ключ отсутствует и поэтому применение комплементарных ключей резко сокращает расход энергии источника питания и облегчает тепловой режим микросхем.

Ток комплементарного ключа отличен от нуля только в режиме переключения. Пусть, для примера, состояние ключа меняется под воздействием положительного перепада входного сигнала (от  $u_{BX} = U^- = 0$  до  $u_{BX} = U^+ = E$ ). Первоначально  $T_1$  закрыт, а  $T_2$  открыт, и на выходе присутствует высокий уровень напряжения  $u_{BMX} = U^+ = E$ . При  $u_{BX} > U_{\Pi OP_{-1}}$  ( $U_{\Pi OP_{-1}}$  — пороговое напряжение транзистора  $T_1$ ) возникает ток  $i_C$ , величину которого определяет транзистор  $T_1$  (рис. 2.21). В соответствии с (2.4) напряжение насыщения  $T_1$ , которое определяет ток на пологом участке выходных статических характеристик,  $U_{CH\_HAC_{-1}} = u_{3H_{-1}} - U_{\Pi OP_{-1}}$ . На основании (2.3)

$$i_C = i_C(u_{CH_-1}) \approx i_C(U_{CH_-HAC_-1}) = 0.5b_1(u_{3H_-1} - U_{\Pi OP_-1})^2 = 0.5b_1(u_{BX} - U_{\Pi OP_-1})^2.$$

Здесь  $b_1$ ,  $u_{3U_{-1}}$  и  $u_{CU_{-1}}$  — удельная крутизна, управляющее напряжение затвористок и напряжение сток—исток транзистора  $T_1$ .

Дальнейший рост  $u_{BX}$  перемещает рабочие токи и напряжения обоих транзисторов на пологие участки выходных статических характеристик, где

$$i_C = 0.5b_1(u_{BX} - U_{\Pi OP_{-1}})^2 = 0.5b_2(u_{3H_{-2}} - U_{\Pi OP_{-2}})^2 = 0.5b_2(u_{BX} - E - U_{\Pi OP_{-2}})^2.$$

(2.6)

Здесь  $b_2$  и  $u_{3H_2}$  и  $U_{\Pi OP_2}$  — удельная крутизна, управляющее и пороговое напряжения транзистора  $T_2$ . (Напомним, что пороговое напряжение p-канального транзистора  $U_{\Pi OP_2} < 0$ .)

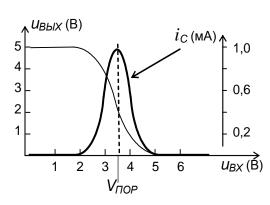

Рис. 2.22. Переключательная характеристика МДП-ключа

При дальнейшем увеличении  $u_{BX}$  транзистор  $T_1$  продолжает открываться и закрывается транзистор  $T_2$ . Ток ключа вплоть до перехода в новое статическое состояние ( $T_1$  открыт,  $T_2$  закрыт,  $u_{BMX} = 0$ ) будет определяться транзистором  $T_2$ :

$$i_C = 0.5b_2(u_{BX} - E - U_{HOP_2})^2$$

.

Переключательная характеристика комплементарного ключа приведена на

рис. 2.22. Порог переключения находится из (2.6) и равен

$$V_{\Pi OP} = \left[ U_{\Pi OP\_1} + \sqrt{\frac{b_2}{b_1}} (E + U_{\Pi OP\_2}) \right] / \left( 1 + \sqrt{\frac{b_2}{b_1}} \right).$$

Обычно  $b_2/b_1 \approx 1$  и

$$V_{\Pi OP} \approx 0.5(E + U_{\Pi OP_{-1}} + U_{\Pi OP_{-2}}).$$

При  $|U_{\Pi OP_{-1}}| = |U_{\Pi OP_{-2}}|$  порог переключения  $V_{\Pi OP} \approx 0.5E$ .

Описанный процесс смены состояния МДП-ключа не учитывает его инерционности, т. е. параметров транзисторов, которые влияют на скорость переключения, и прежде всего межэлектродных емкостей. Как уже отмечалось, в статическом режиме ток через комплементарный ключ отсутствует. Время пребывания ключа под током зависит от времени (скорости) переключения. Эти обстоятельства важны для СБИС, уровень интеграции которых достигает десятков миллионов вентилей на кристалл.

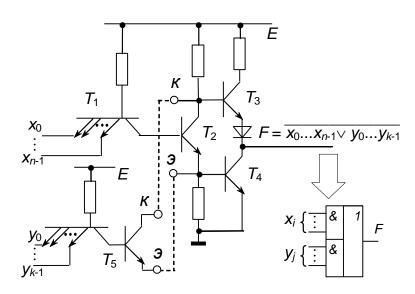

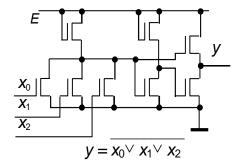

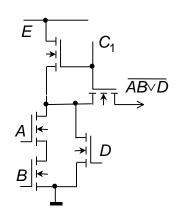

Погика на МДП-структурах классифицируется по типу используемых ключей — n-канальных (n-МОП, или n-МДП), p-канальных (p-МОП, или p-МДП) и комплементарных (КМОП, или КМДП). Различие транзисторов по типу канала (n- или p-канал, канал встроенный или индуцированный) не вносит принципиальных отличий в схему построения логических элементов — логические операции выполняются на сети ключевых транзисторов, например так, как показано на рис. 2.23.

Рис. 2.23. Логический элемент на МОП-транзисторах

Рис. 2.24. Базовый логический элемент на МОП-транзисторах

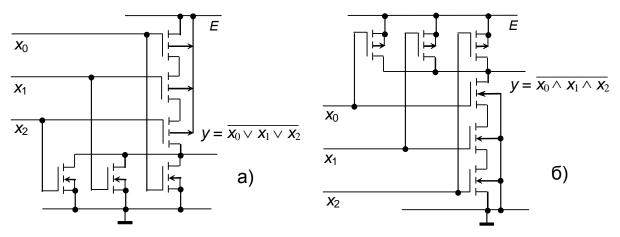

Логический узел базового элемента n-МДП- и p-МДП-логики (рис. 2.24) строится на параллельных транзисторах. В каждом элементе имеется согласующий каскад, который состоит из инвертора и выходного ключа на двух управляемых однотипных транзисторах.

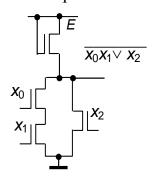

Рис. 2.25. Базовые элементы ЗИЛИ-НЕ (а) и ЗИ-НЕ (б) КМДП-логики

КМДП-логике (КМДПЛ) также используются последовательные соединения ключевых транзисторов. Специфика работы комплементарного ключа такова, что логические элементы на их основе не нуждаются в цепях согласования и разные логические узлы могут быть соединены друг с другом непосредственно. Базовый логический элемент (рис. 2.25) состоит из двух групп транзисторов: *п*-канальной и *p*-канальной. В (рис. 2.25а) ИЛИ-НЕ *п*-канальные транзисторы элементе включены параллельно и в положительной логике выполняют операцию ИЛИ. Ту же операцию выполняет и ряд из последовательных p-канальных транзисторов, т. к. по отношению к ним положительная для n-канальных транзисторов логика становится отрицательной. В элементе И-НЕ (рис. 2.25б), наоборот, nтранзисторы соединены последовательно, р-канальные канальные параллельно.

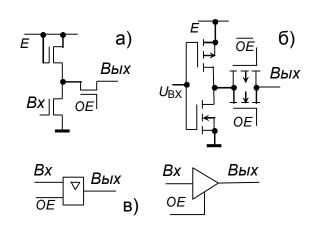

#### 2.3.9. Элементы с тремя состояниями

При построении многокомпонентных цифровых систем в обеспечении бесконфликтного взаимодействия устройств в составе системы с другими особенно тогда, когда взаимодействие осуществляется с использованием одних и тех же линий связи. В этом случае источником информации может быть только одно устройство, а другие потенциально возможные источники должны быть в отключенном от линий связи состоянии. Механизмом отключения являются элементы с тремя переводящие устройства состояниями, выходы неактивного высокоимпедансное (третье в дополнение к «0» и «1») состояние. Перевод входов/выходов одних схем в высокоимпедансное состояние дает возможность передавать информацию от других (к другим) по совместно используемым линиям.

Рис. 2.26. Элементы с тремя состояниями на МДП-транзисторах (а, б) и их условные обозначения (в)

Элемент c тремя состояниями выхода кроме логического состояния 0 и имеет состояние «отключено», котором ток его выходной цепи пренебрежимо мал (состояние с высоким выходным импедансом). В это (третье) элемент переводится состояние управляющим сигналом специальным (на рис. 2.26 сигналом OE – Output Enable). Наиболее просто вентили с тремя состояниями выполняются на МДП-транзисторах. В n-МДП или p-МДП-схемах роль элемента с тремя состояниями может выполнять передающий транзистор (рис. 2.26а), а в

КМДП-схемах — пара комплементарных транзисторов с противофазными управляющими сигналами OE и  $\overline{OE}$  на затворах (рис. 2.26б). Вместо электронного ключа в элементах с тремя состояниями (рис. 2.26а, б) может быть логический узел, построенный так, как это было показано в разделе 2.3.8.

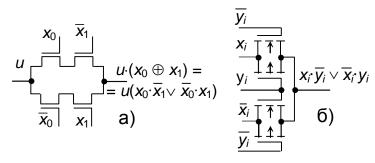

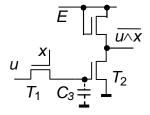

# 2.3.10. Особенности логических операций на передающих транзисторах. Динамические элементы

Сеть передающих транзисторов может быть использована по-разному, в том числе и для выполнения логических операций. Примером может послужить несложная сеть из двух параллельных ветвей, состоящих из однотипных последовательно соединенных каналов, для операции «исключающее ИЛИ» (рис. 26а). Подобную функцию можно выполнить и на передающих комплементарных транзисторах (рис. 2.26б).

Рис. 2.26. Пример логических операций с помощью передающих МДП-транзисторов

Рис. 2.27. Простейший динамический элемент на передающем и ключевом МДП-транзисторах

Другой способ реализации логических функций состоит в сочетании ключевых и передающих транзисторов. Однако в этом случае сеть приобретает новое качество, т. к. логические функции по-разному выполняются передающими и ключевыми транзисторами. В первом случае значение функции

зависит от возможности протекания тока, тогда как во втором — от уровня напряжения. Кроме того, потенциал затвора ключевого транзистора зависит от накопленного заряда и может сохраняться в отсутствие тока.

Пусть, например, ток к затвору подводится через передающий транзистор  $T_1$  (рис. 2.27), но затем цепь для протекания тока разрывается. Это ведет к изоляции затвора ключевого транзистора  $T_2$ , и заряд на нем будет существовать некоторое время, зависящее от скорости разряда емкости затвора  $C_3$  через сопротивление утечки  $R_y$ . Время разряда  $\tau_P = C_3 R_y$  составляет сотни миллисекунд, что несопоставимо с временем переключения  $\tau_\Pi$  (доли или несколько наносекунд). При достаточно частых (с частотой  $f_\Pi >> 1/\tau_P$ ) переключениях емкость затвора может выполнять функцию задержки или динамического элемента памяти. В простейшем случае динамический элемент состоит из передающего транзистора и инвертора (рис. 2.27).

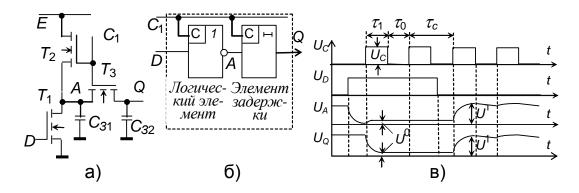

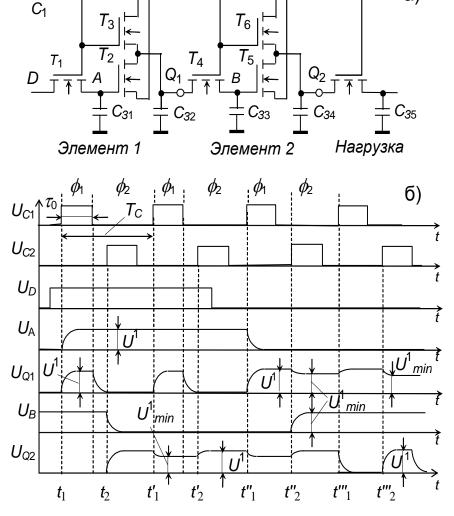

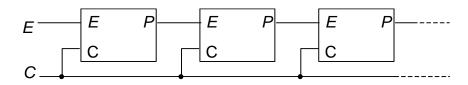

#### Двухфазные динамические элементы

Рассмотрим подробнее работу элемента, представленного на рис. 2.27. Для этого переставим местами инвертор и передающий транзистор (рис. 2.28). Элементы памяти представлены емкостями затвор—исток  $C_{31}$  и  $C_{32}$  передающего  $T_3$  и следующего за ним (не показанного на рисунке) ключевого транзистора, являющегося нагрузкой  $T_3$ . На затворы нагрузочного транзистора  $T_2$  и передающего транзистора  $T_3$  подается последовательность синхроимпульсов  $C_1$ . Работа элемента иллюстрируется временными диаграммами на рис. 2.28в.

При возрастании потенциала  $U_{BX}$  на входе D выше порога переключения  $V_{II}=U_{IIOP}$ , где  $U_{IIOP}$  — пороговое напряжение МДП-транзистора, открывается транзистор  $T_1$  и емкость  $C_{31}$  разряжается до низкого потенциала  $U_A\approx 0$ . При поступлении синхроимпульса амплитудой  $U_C>U_{IIOP}$  открываются транзисторы  $T_2$  и  $T_3$  и на выходе Q устанавливается низкий потенциал  $U^0=U_{OCT_1}+U_{OCT_2}$ , где  $U_{OCT}$  — остаточное напряжение между стоком и истоком  $T_1$  и  $T_3$ , работающих в крутой области (область 1 на рис. 2.18в) стоковых характеристик, которые описываются выражением (2.3). При этом нагрузочный транзистор  $T_2$  работает в пологой области (область 2 на рис. 2.18в) стоковых характеристик и для него ток стока, а значит, и ток инвертора определяется значением  $i_C\approx i_C(u_{CH_2})$  при  $u_{CH_2}=U_{CH_{AC}}$ . В силу этого

$$i_C \approx 0.5b_2 \cdot (U_C - U_{\Pi OP_2})^2.$$

(2.6)

Рис. 2.28. Схема двухфазного динамического элемента «с отношением» (а), его структура (б) и временные диаграммы (в)

Так как через транзистор  $T_3$  ток не протекает, то  $U_{OCT\_3} \approx 0$ . Поэтому с учетом (2.3), (2.6) и того, что для открытого транзистора  $T_1 u_{CU\_1} << U_{\Pi OP\_1}$  и  $u_{3U\_1} = U^1$ , а для открытого транзистора  $T_2 u_{3U\_2} \approx U_{\rm C}$ , получим

$$U^{0} = U_{OCT_{-1}} = i_{C} r_{CH_{-1}} = 0.5b_{2}(U_{C} - U_{\Pi OP_{-2}})^{2}/b_{1}(U^{1} - U_{\Pi OP_{-1}}).$$

(2.7)

Здесь  $b_1$ ,  $b_2$  — удельная крутизна транзисторов  $T_1$  и  $T_2$ ,  $U_{\Pi OP_2} = U_{\Pi OP_1} = U_{\Pi OP}$ ,  $U^1$  — высокий, соответствующий логической «1», уровень напряжения. По окончании синхроимпульса, когда устанавливается потенциал  $U_C = 0$ , транзисторы  $T_2$  и  $T_3$  запираются. Заряд на емкости  $C_{32}$  и соответственно низкий уровень потенциала  $U^0$  на выходе Q будут сохраняться в течение времени хранения  $t^0_{XP}$ , длительность которого определяется процессом заряда емкости  $C_{32}$  токами утечки:  $t_3 = R_y C_{32}$ , где  $R_y$  — сопротивление утечки. При типовых значениях  $C_{32} = 0,1...1$  пФ,  $R_y = 10^8...10^9$  Ом получим  $t_3 = 10...1000$  мкс. Чтобы не произошло потери информации, т. е. ложного переключения элемента, необходимо подать новый синхроимпульс  $C_1$  раньше, чем потенциал  $U_{BbIX}$  вследствие заряда  $C_{32}$  возрастет до уровня  $U_{\Pi OP}$ , т. е. спустя время

$$\tau_0 < t^0_{XP} \approx t_3 \cdot (U_{HOP}/E).$$

(2.8)

Очередной синхроимпульс, открывая  $T_2$  и  $T_3$ , обеспечивает разряд  $C_{32}$  до потенциала  $U_{BMX} = U^0$  и восстанавливает информацию.

При уменьшении потенциала на входе D до низкого уровня  $U_{BX} = U^0 < U_{\Pi O P}$  транзистор  $T_1$  запирается. При поступлении синхроимпульса  $C_1$  через открывающиеся транзисторы  $T_2$  и  $T_3$  емкости  $C_{31}$  и  $C_{32}$  заряжаются до высокого потенциала  $U_{B b l X} = U^1 = U_C - U_{\Pi O P}$ . Если синхроимпульс имеет достаточно большую амплитуду  $U_C > E + U_{\Pi O P}$ , то выходное напряжение достигает величины  $U^1 = E$ . По окончании синхроимпульса  $T_2$  и  $T_3$  запираются и потенциал на выходе поддерживается в течение времени  $t^1_{XP}$ , пока емкость  $C_{32}$  сохраняет достаточный заряд. Поэтому необходимо обеспечить выполнение соотношения

$$\tau_0 < t^1_{XP} \approx t_{3} \cdot (U^1 - U_{IIOP})/U^1.$$

(2.9)

Следующий импульс  $C_1$  открывает транзисторы  $T_2$  и  $T_3$  и подзаряжает емкости до уровня  $U^1$ . При выполнении (2.8) и (2.9) динамический элемент ведет себя как синхронизируемый бистабильный элемент — триггер. Имеются два режима его работы: при  $C_1 = 1$  — прием (запись) информации (с инверсией), при  $C_1 = 0$  — ее хранение.

Для обеспечения достаточной помехоустойчивости динамических элементов следует уменьшить  $b_2/b_1$  — отношение удельной крутизны нагрузочного и управляющего транзисторов, чтобы выполнялось условие  $U^0 < U_{\Pi OP} - U_{\Pi}$ , где  $U_{\Pi}$  — требуемое значение помехоустойчивости. Используя (2.7), получаем следующее ограничение на величину  $b_2/b_1$ :

$$b_2/b_1 \le 2(U^1 - U_{\Pi OP})(U_{\Pi OP} - U_{\Pi})/(U_C - U_{\Pi OP})^2.$$

Рис. 2.29. Двухфазный динамический элемент И-ИЛИ-НЕ

При типовых значениях  $U^1$ ,  $U_C$  и  $U_{\Pi OP}$  получаем следующее требование:  $b_2/b_1 \le 0,1$ . На практике это достигается использованием МДП-транзисторов с различными геометрическими размерами. Так как удельная крутизна пропорциональна отношению ширины канала к его длине (W/L), то транзистор  $T_1$  изготавливается с коротким и широким каналом, а транзистор  $T_2$  — с более длинным и узким.

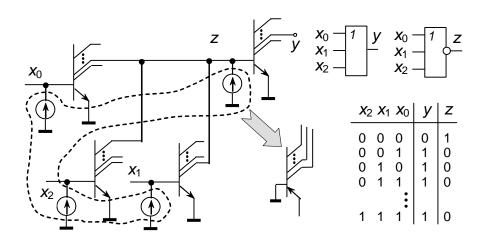

Используя параллельное и последовательное включение управляющих транзисторов  $T_1$ , подобно тому, как это показано на рис. 2.23 и 2.24, получаем динамические элементы, выполняющие заданную логическую операцию, например, И-ИЛИ-НЕ (см. рис. 2.29).

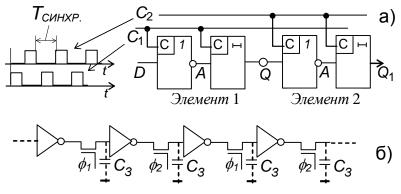

Рис. 2.30. Структура динамического триггера (a) и последовательная цепь динамических элементов (б)

При соединении динамических элементов (рис. 2.30) необходимо в последовательно включенных элементах (инвертор плюс передающий канал) разделить во времени фазы приема и хранения информации. Для этого используются две последовательности синхроимпульсов  $C_1$  и  $C_2$ . Каждый такт работы устройства, соответствующий одному периоду синхроимпульсов  $T_{\text{СИНХР}}$ , состоит из двух фаз ( $\phi_1$  и  $\phi_2$ ). В одной фазе происходит переключение

элементов 1 (импульсами  $C_1$ ) при сохранении состояния элементов 2. Во второй фазе импульсами  $C_2$  переключаются элементы 2, а элементы 1 находятся в режиме хранения.

В рассмотренном динамическом элементе предъявляются противоречивые требования к параметрам транзисторов  $T_1$  и  $T_2$ . Во многих случаях предпочтительнее использовать динамические элементы «без отношения», параметры которых не зависят от отношения  $b_2/b_1$ .

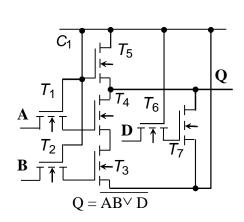

#### Двухфазные динамические элементы «без отношения»

Вариант динамического элемента «без отношения» показан на рис. 2.31. Рассмотрим работу двух последовательно соединенных элементов этого типа, используя временные диаграммы на рис. 2.31б. Пусть в исходном положении на вход D подан низкий потенциал  $U_D \approx 0$ . Тогда на емкостях  $C_{31}$ ,  $C_{32}$ ,  $C_{34}$  низкий потенциал  $U_A = U_{Q1} = U_{Q2} = 0$ , а на  $C_{33}$  – высокий потенциал  $U_B = U^1$ . Если на вход D поступит высокий потенциал  $U_D = U^1 > U_{ПОP}$ , то при подаче синхроимпульса  $C_1$  (фаза  $\phi_1$ ) транзистор  $T_1$  откроется, емкость  $C_{31}$  зарядится до  $U_A \approx U^1$ . Транзисторы  $T_2$  и  $T_3$  открываются, и емкость  $C_{32}$  заряжается до потенциала  $U_{Q1} = U^1 = U_C - U_{ПОP}$ .

После окончания синхроимпульса  $C_1$  емкость  $C_{32}$  через открытый транзистор  $T_2$  разряжается до  $U_{\rm Q1}\approx 0$ . При поступлении синхроимпульса  $C_2$  (фаза  $\phi_2$ ) открываются транзисторы  $T_4$  и  $T_6$ . Емкость  $C_{33}$  через открытые  $T_2$  и  $T_4$  разряжается до  $U_B\approx 0$ , и транзистор  $T_5$  запирается. В дальнейшем при неизменном  $U_D=U^1$  потенциал на емкостях  $C_{31}$  и  $C_{34}$  сохраняется высоким, а потенциал  $C_{33}$  — низким. Емкость  $C_{32}$  при поступлении каждого синхроимпульса  $C_1$  заряжается до  $U_{\rm Q1}=U^1$ , а после его окончания разряжается до  $U_{\rm Q1}=0$ . Низкий потенциал  $U_B=0$  сохраняется на емкости  $C_{33}$ , и транзистор  $T_5$  остается закрытым. При поступлении импульса  $C_2$  емкость  $C_{34}$  заряжается до  $U_{\rm Q2}=U^1$ . При поступлении импульса  $C_1$  заряд емкости  $C_{34}$  распределяется между ней и емкостью  $C_{35}$  в элементе-нагрузке. На выходе  $Q_2$  устанавливается уровень  $U^1_{min}$ , который должен быть достаточным для отпирания следующего МДП-транзистора:

$$U_{min}^{1} = (U_C - U_{\Pi OP}) C_{34}/(C_{34} + C_{35}) \ge U_{\Pi OP}.$$

(2.10)

Выполнение соотношения (2.10) достигается соответствующим выбором амплитуды синхроимпульсов  $U_C$ . Для снижения требуемой величины  $U_C$  топология элемента проектируется так, чтобы обеспечить достаточно большое отношение  $C_{34}/C_{35} = C_{32}/C_{33} \ge U_{\Pi OP}/(U_C - 2U_{\Pi OP})$ .

a)

$C_2$

Рис. 2.31. Схема динамического триггера на двухфазных элементах «без отношения» (а) и его временные диаграммы (б)

После установления на входе потенциала  $U_D \approx 0$  и поступления синхроимпульса  $C_1$  (фаза  $\phi_1$ ) емкость  $C_{31}$  разряжается через транзистор  $T_1$  до  $U_A \approx 0$ , и транзистор  $T_2$  запирается. Емкость  $C_{32}$  через открытый транзистор  $T_3$  заряжается до потенциала  $U_{Q1} = U^1$ , который сохраняется после окончания синхроимпульса  $C_1$ . При поступлении синхроимпульса  $C_2$  (фаза  $\phi_2$ ) открывается транзистор  $T_4$  и заряд емкости  $C_{32}$  распределяется между емкостями  $C_{32}$  и  $C_{33}$ . В результате на емкостях  $C_{32}$  и  $C_{33}$  устанавливается потенциал  $U_{Q1} \approx U_B \approx U^1_{min}$ . На выходе второго элемента  $Q_2$  формируется последовательность импульсов амплитудой  $U^1$ , каждый из которых образуется при поступлении импульса  $C_2$ . Аналогично работают элементы и в том случае, когда на вход вместо постоянного потенциала  $U_D = 0$  поступает последовательность импульсов, синхронизированных с синхроимпульсами  $C_2$ .

Таким образом, значение  $U_Q = U^0$  на выходе динамических элементов поддерживается только во время паузы между синхроимпульсами соответствующей последовательности ( $C_1$  или  $C_2$ ), а в течение действия

синхроимпульса  $U_{\rm Q}=U^{\rm l}$ . Однако вследствие двухфазной синхронизации последующий элемент воспринимает только истинное значение, соответствующее сигналу на входе предыдущего элемента во время паузы между синхронизирующими импульсами. Возникновение на выходе «ложных» импульсов амплитудой  $U^{\rm l}$  не совпадает во времени с режимом записи информации в последующий элемент и поэтому не влияет на работу устройства.

Рис. 2.32. Схема двухфазного динамического элемента И-ИЛИ-НЕ «без отношения»

Логические функции на элементах «без отношения» реализуются так же, как и на элементах с отношением, комбинацией последовательного и параллельного включений передающих транзисторов с подключением их к затворам ключевых транзисторов (рис. 2.32).

Рассмотренные примеры динамических исчерпывают элементов не вариантов ИΧ приведены основном построения И ДЛЯ иллюстрации тех функциональных возможностей, которые приобретаются совместном использовании передающих ключевых транзисторов. К таким возможностям относится использование емкости затвора МДПтранзистора в качестве элемента памяти, что имеет большое значение при создании СБИС.

### 3. Функциональные узлы комбинационного типа

Функциональные узлы выполняют типовые для цифровых устройств (ЦУ) микрооперации. Микрооперации соответствуют низшему иерархическому уровню внутреннего языка цифрового устройства, они обозначены в этом языке и не содержат других операций, кроме обозначенных в нем. Как и все цифровые устройства вообще, функциональные узлы делятся на комбинационные и последовательные. В дальнейшем комбинационные узлы будем обозначать через КЦ (комбинационные цепи), а последовательные – через АП (автоматы с памятью). Различия между КЦ и АП имеют фундаментальный характер.

Выходные величины КЦ зависят только от текущего значения входных величин (аргументов). Предыстория не имеет значения. После завершения переходных процессов в КЦ на их выходах устанавливаются величины, на которые характер переходных процессов влияния не оказывает. С этой точки зрения переходные процессы в КЦ не опасны. Но в ЦУ в целом КЦ функционируют совместно с АП, что кардинально меняет ситуацию. Во время переходных процессов на выходах КЦ появляются временные сигналы, не предусмотренные описанием работы КЦ и называемые рисками. Со временем они исчезают и выход КЦ приобретает значение, предусмотренное логической формулой, описывающей работу цепи. Однако риски могут быть восприняты элементами памяти АП, необходимое изменение состояния которых может радикально изменить работу ЦУ. Примером служат рассмотренные выше динамические элементы, для работы которых важна синхронизация.

Некоторые из устройств комбинационного типа (полный дешифратор, демультиплексор и мультиплексор) были рассмотрены ранее (см. начало раздела 2). Причиной послужило то, что с помощью этих КЦ реализуется СДНФ логических выражений. Как продолжение рассмотрим комбинационные цепи, предназначением которых является выполнение логических функций, свойственных устройствам, входящим в состав цифровых вычислительных систем.

# 3.1. Арифметические устройства

## 3.1.1. Двоичные сумматоры

Операция суммирования — это одна из наиболее часто встречающихся операций в цифровой технике. Пусть слагаемыми являются два n-разрядных двоичных числа

$$X = (x_{n-1}...x_1x_0) = x_{n-1}2^{n-1} + x_{n-2}2^{n-2} + x_12^1 + x_02^0$$

и  $Y = (y_{n-1}...y_1y_0) = y_{n-1}2^{n-1} + y_{n-2}2^{n-2} + y_12^1 + y_02^0$ .

$$\frac{6}{0}$$

$\frac{5}{1}$   $\frac{4}{1}$   $\frac{3}{1}$   $\frac{2}{1}$   $\frac{1}{1}$   $\frac{1$

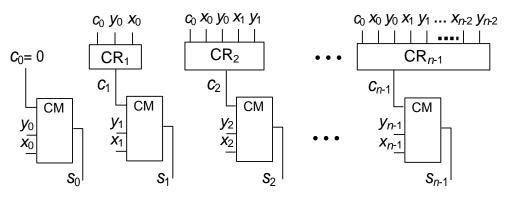

Определим алгоритм, по которому будет осуществляться операция суммирования. Сделаем это на примере, когда X = 25, Y = 29, а n = 6 (рис. 3.1). Суммируются все разряды, начиная с младшего. Правило суммирования заключается в следующем:

1) перенос в (*i*+1)-й (следующий)

разряд из *i*-го (предыдущего)  $c_{i+1} = 1$  (истина), если  $\partial se$  или mpu величины из  $a_i$ ,  $b_i$  и  $c_i$  истинны (равны 1), т.е.

$$c_{i+1} = (x_i y_i c_i \vee x_i y_i \bar{c}_i) \vee (x_i \bar{y}_i c_i \vee \bar{x}_i y_i c_i) = x_i y_i \vee (x_i \oplus y_i) \cdot c_i. \tag{3.1}$$

Знак ⊕ обозначает операцию

$$x_i \oplus y_i = x_i \bar{y}_i \vee \bar{x}_i y_i$$

,

называемую сумма по модулю 2 или исключающее ИЛИ. Из (3.1) получаются более простые выражения для формирования переноса  $c_{i+1}$ :

$$c_{i+1} = x_i y_i \lor x_i c_i \lor y_i c_i =$$

(в базисе И-ИЛИ)

=  $\overline{x_i y_i \cdot \overline{x_i c_i} \cdot \overline{y_i c_i}}$  (в базисе И-НЕ); (3.2)

2) значение *i*-го разряда суммы  $s_i = 1$  (истинно), если истинно (равно 1) нечетное число величин  $x_i$ ,  $y_i$  и  $c_i$ :

$$s_i = (x_i \oplus y_i) \oplus c_i = x_i \oplus y_i \oplus c_i , \qquad (3.3)$$

или

$$s_{i} = x_{i}y_{i}c_{i} \vee \bar{x}_{i}\bar{y}_{i}c_{i} \vee x_{i}\bar{y}_{i}\bar{c}_{i} \vee \bar{x}_{i}y_{i}\bar{c}_{i} =$$

(в базисе И-ИЛИ)

$$= \overline{x_{i}y_{i}c_{i}} \cdot \overline{x_{i}\bar{y}_{i}c_{i}} \cdot \overline{x_{i}\bar{y}_{i}\bar{c}_{i}} \cdot \overline{x_{i}y_{i}\bar{c}_{i}}$$

(в базисе И-НЕ);

3) значение переноса в младший (i = 0) разряд  $c_0 = 0$ .

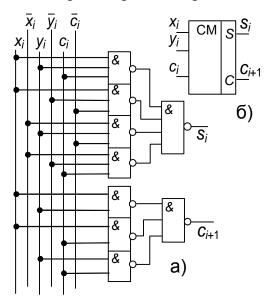

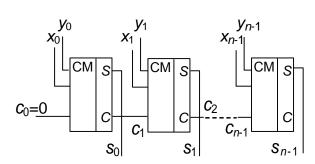

*Одноразрядный сумматор* имеет три входа (два слагаемых и перенос из предыдущего разряда) и два выхода (сумма и перенос в следующий разряд).

Непосредственное воспроизведение выражений (3.2) и (3.4) для сумматора в базисе И-НЕ приводит к применению трех элементов 2И-НЕ, пяти элементов 3И-НЕ и одного элемента 4И-НЕ (рис. 3.2).

Логику работы сумматора можно построить на основе таких сочетаний значений  $x_i$ ,  $y_i$  и  $c_i$ , при которых сумма и перенос будут равны ложны:

$$\bar{s}_i = \bar{x}_i c_{i+1} \vee \bar{y}_i c_{i+1} \vee \bar{c}_i c_{i+1} \vee \bar{x}_i \bar{y}_i \bar{c}_i,

\bar{c}_{i+1} = \bar{x}_i \bar{y}_i \vee \bar{x}_i \bar{c}_i \vee \bar{y}_i \bar{c}_i,$$

(3.5)

Соответствующая (3.5) логическая схема сумматора в базисе И-ИЛИ-НЕ представлена на рис. 3.3.

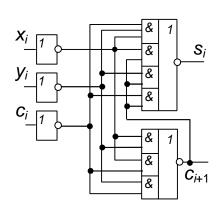

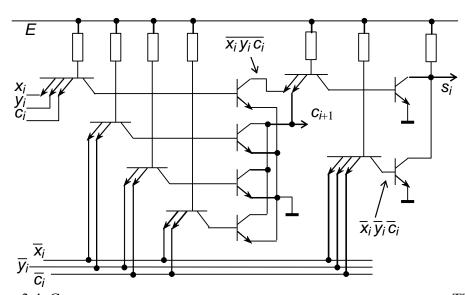

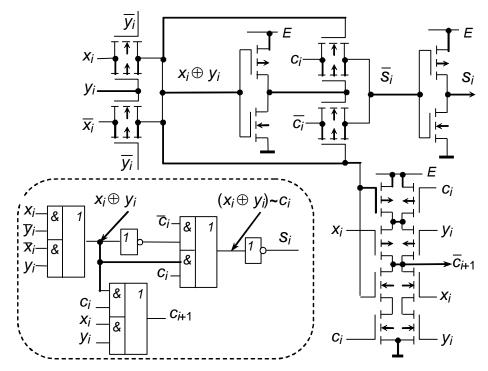

Выбор логики работы сумматора зависит от того, какая элементная база используется для реализации логических операций. В качестве примеров схемно-ориентированной логики рассмотрим формирование суммы и образование переноса в транзисторно-транзисторной логике и логике на комплементарных транзисторах.

Рис. 3.2. Логическая схема в базисе И-НЕ (а) и условное обозначение (б) одноразрядного сумматора

Рис. 3.3. Одноразрядный сумматор в базисе И-ИЛИ-НЕ

Для первого случая удобно воспользоваться выражениями

$$s_i = \overline{(x_i y_i c_i) \cdot c_{i+1} \vee (\overline{x}_i \overline{y}_i \overline{c}_i)}$$

(3.6)

И

$$\bar{c}_{i+1} = \bar{x}_i \bar{y}_i \vee \bar{x}_i \bar{c}_i \vee \bar{y}_i \bar{c}_i, \tag{3.7}$$

Рис. 3.4. Схемная реализация одноразрядного сумматора на основе ТТЛ

которые можно получить из (3.5), применив теорему де Моргана. Логические выражения (3.6) и (3.7) реализуются с помощью многоэмиттерных и параллельно включенных биполярных транзисторов (рис. 3.4)

Выражение (3.3) для суммы можно преобразовать к виду

$$\overline{s_i} = \overline{(x_i \oplus y_i)} \cdot \overline{c_i} \vee (x_i \oplus y_i) \cdot c_i, \tag{3.8}$$

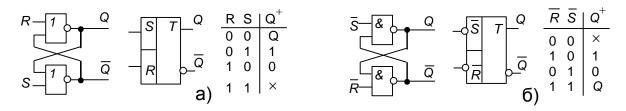

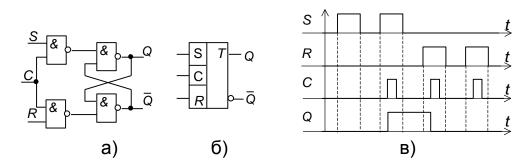

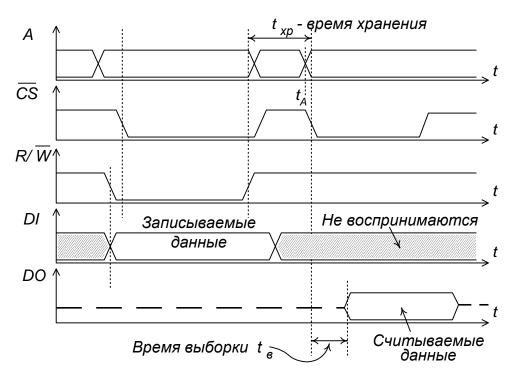

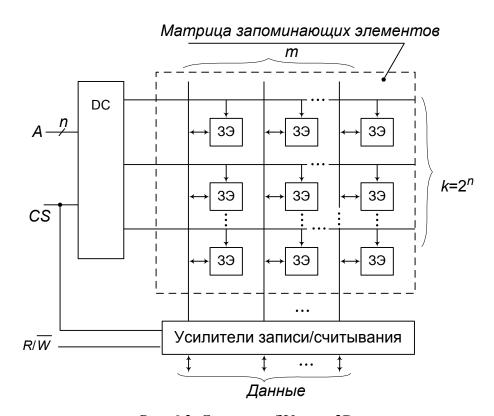

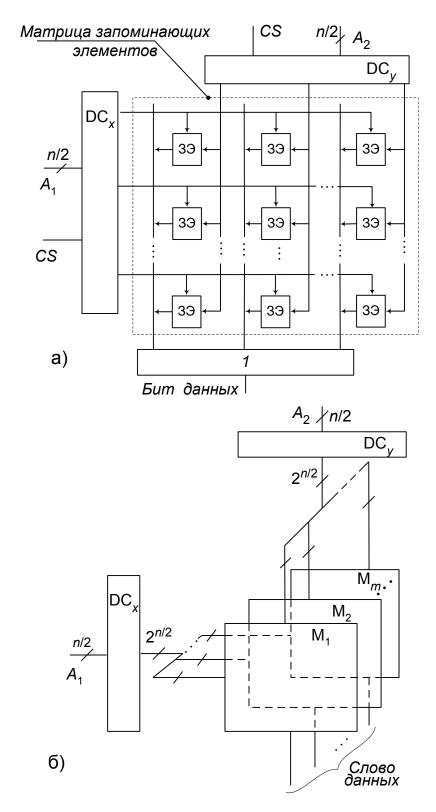

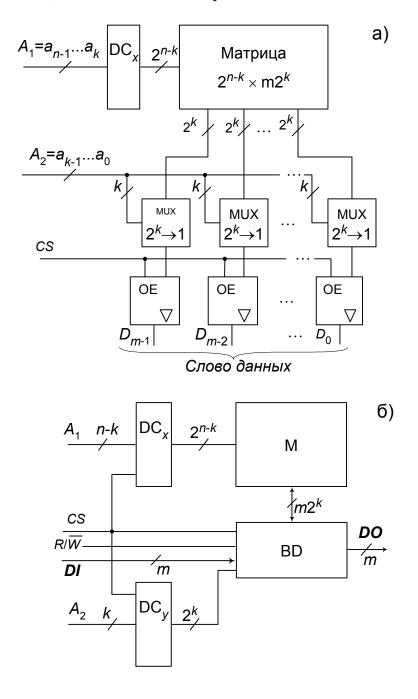

$$x \oplus y = x\overline{y} \vee \overline{x}y = \overline{x\overline{y}} \cdot \overline{\overline{x}y} = \overline{(\overline{x} \vee y) \cdot (x \vee \overline{y})} = \overline{x \cdot y \vee \overline{x} \cdot \overline{y}} = \overline{x \sim y}.$$